## High Performance TFT-LCD Graphics Controller

# Introduction

LT768x are an series high-performance TFT-LCD graphics accelerated display chip. Its main function is to assist MCU to display the contents of the TFT screen to the TFT Driver. It provides graphics acceleration, PIP (picture-in-picture), geometry graphics and other functions, in addition to enhance the display efficiency, Also greatly reduces the MCU processing graphics display time spent. LT768x also supports a very broad display resolution, can be from 320\*240(QVGA) to 1280\*1024(SXGA), the display is supported 16/18/24bits RGB interface.

LT768x supports a variety of MCU interface, including SPI, I2C serial port, or 8-bit, 16-bit parallel interface. In order to achieve multi-layers high-resolution display effect, LT768x embedded a 64MB or 128MB Display

RAM. This Display Memory can support 16M color display from 2 gray to 1bit per pixel to up to 24bits per pixel. At the same time to reduce the animation display MCU in the software operation burden. LT768x built-in geometry drawing engine, supporting the painting point, drawing Line, drawing curve, ellipse, triangle, rectangle, rounded rectangle and other functions. The embedded hardware graphics Acceleration Engine (BTE) provides the command type of graphics operations, such as display rotation, mirror shot, The painting (PIP/Master-Sub Screen) and graphics mixed transparent display and other functions, enhance the display of the product performance, so can greatly reduce the MCU software operating burden. if use the high-speed SPI interface, then it can reduce the MCU I/O port needs, without to upgrade the MCU for TFT display. LT768x powerful display function is very suitable for the electronic products with TFT-LCD screen, such as

equipment, medical equipment, human-computer interface, testing equipment and other products.

home appliances, multi-functional business machines, industrial equipment, industrial control, electronic

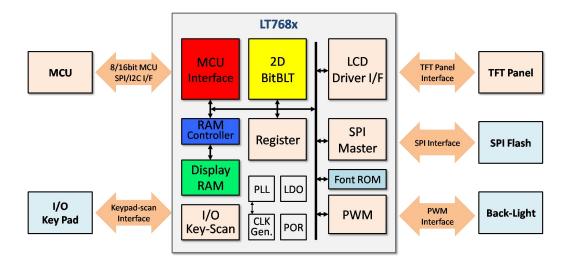

# Internal Block Diagram

Figure A-1: Internal Block Diagram

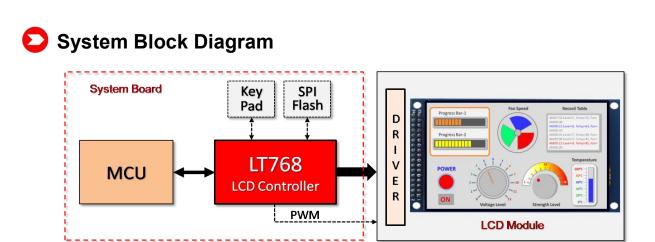

Figure A-2: LT768x Designed on System Board

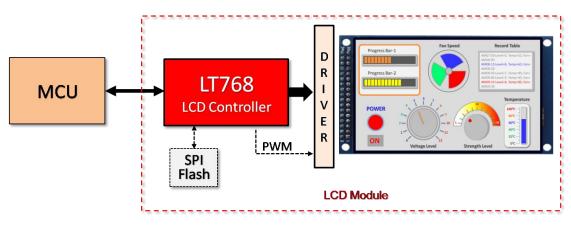

Figure A-3: LT768x Designed on TFT-LCD Module

# 🔁 Model Name

**7**LT768x

| Model Name | Package      | Embedded<br>Display RAM | Resolution<br>(Max.) | Colors |

|------------|--------------|-------------------------|----------------------|--------|

| LT7681     | LQFP-128     | 128Mb                   | 640*480              | 16.7M  |

| LT7683     | LQFP-128     | 128Mb                   | 800*600              | 16.7M  |

| LT7686     | LQFP-128     | 128Mb                   | 1280*1024            | 16.7M  |

| LT7680A    | QFN-68 (8*8) | 64Mb                    | 800*600              | 262K   |

| LT7680B    | QFN-68 (8*8) | 64Mb                    | 480*320              | 262K   |

# *I* LT768x

# Features

### **Host Interface**

- Support Three Types 8/16bits Asynchronous Bus Register Interface (or Memory Data)

- Indirect Intel-80 Bus Interface

- Indirect Motorola-6800 Bus Interface

- Provides Insert Wait State Mechanism on Parallel Host Cycle

- Support I<sup>2</sup>C Bus Interface

- Support Various SPI Protocol. Ex. 3 or 4-wire SPI

### **Display Data Formats**

- 1bpp: Monochrome Data (1-bit/Pixel)

- 8bpp: RGB 3:3:2 (1-byte/Pixel)

- 16bpp: RGB 5:6:5 (2-byte/Pixel)

- 24bpp: RGB 8:8:8 (3-byte/Pixel or 4-byte/Pixel)

- Index 2:6 (64 Index Colors/Pixel with Opacity Attribute)

- αRGB 4:4:4:4 (4096 Colors/Pixel with Opacity Attribute)

### **Support Panel and Resolution**

- Support 16/18/24-bits RGB Interface Type Panel

- Supported Resolution:

- > QVGA : 320\*240, 16/18/24-bit LCD Panel

- > WQVGA: 480\*272, 16/18/24-bit LCD Panel

- > VGA : 640\*480, 16/18/24-bit LCD Panel

- > WVGA : 800\*480, 16/18/24-bit LCD Panel

- > SVGA : 800\*600, 16/18/24-bit LCD Panel

- > QHD : 960\*540, 16/18/24-bit LCD Panel

- > WSVGA : 1024\*600, 16/18/24-bit LCD Panel

- > XGA : 1024\*768, 16/18/24-bit LCD Panel

- > SXGA : 1280\*1024, 16/18/24-bit LCD Panel

### **Display Functions**

- Multiple Display Buffer: Multi buffering allows the main display window to be switched among buffers. Multi buffering allows a simple animation display to be performed by switching the buffers

- Horizontal/Vertical Flip Display: Vertical Flip display functions are available for image data reads. PIP window will be disabled if flip display function enable

- Mirror and Rotation Functions are Available for Image Data Writes

- Provide four User-defined 32\*32 Pixels Graphic Cursor

- Virtual Display: Virtual display is available to show an image which is larger than LCD panel size. The image may scroll easily in any direction

- Picture-in-Picture (PIP) Display: Supported two PIP windows area: Enabled PIP windows are always displayed on top of Main window. The PIP1 window is always on top of PIP2 window

- Wake-up Display: Wake-up Display is available to show the display data quickly which data is stored in Display RAM. This feature is used when returning from the Standby mode or Suspend mode

- Initial Display: Embedded a tiny processor with 12 instructions and use to show display data which stored in the serial flash and need not external MPU participate. It will auto execute after power-on, until program execute complete then handover control rights to external MCU

- Color Bar: It could display color bar on panel directly. Default resolution is 640 dots by 480 dots

### Bit Block Transfer Engine (BTE)

- 2D BTE Engine

- Copy Image with Raster Operators

- Color Depth Conversion

- Solid Fill & Pattern Fill

- Provide User-defined Patterns with 8\*8 Pixels or 16\*16 Pixels

- Opacity (Alpha-Blend) Control: It blends two images and then generates a new image

- Chroma-Keying Function: Mixes images with applying the specified RGB color according to transparency rate

- Window Alpha-Blending Function: Mixes two images according to transparency rate in the specified region (fade-in and fade-out functions are available)

- Dot Alpha-Blending Function: Mixes images according to transparency rate when the target is a graphics image in the RGB format

### **Display RAM (Frame Buffer)**

- LT7680A/76860B: Embedded 64Mb Display RAM

- LT7681/7683/7686: Embedded 128Mb Display RAM

### Shape Drawing Engine

Provide Smart Drawing Features: Line, Rectangle, Triangle, Polygon, Poly-Line, Circle, Ellipse, Arc, Rounded-Rectangle and Circle-Rectangle

### **Text Features**

- Embedded 8\*16, 12\*24, 16\*32 Character Sets of ISO/IEC 8859-1/2/4/5

- User-defined Characters Support Half Size & Full Size for 8\*16, 12\*24 and 16\*32

- Programmable Text Cursor for Writing with Character

- Character Enlargement Function \*1, \*2, \*3, \*4 for Horizontal/Vertical Direction

- Support Character Rotates 90 Degree

### **PWM Interface**

- Embedded Two 16bits Timers

- One 8-bit Pre-Scalars & One 4bits Divider

- Programmable Duty Control of Output Waveform (PWM)

- Auto Reload Mode or One-Shot Pulse Mode

- Dead-Zone Generator

### **SPI Master Interface**

- Provide DMA Function: Support Direct Data Transfer from External Serial Flash to Frame Buffer

- Compatible with Standard SPI Specifications

- Provides 16bytes Read FIFO and 16bytes Write FIFO

- Provide Interrupt when Tx FIFO was Empty and SPI Tx/Rx Engine Idle

### **I2C Interface**

Support Standard Mode (100kbps) and Fast Mode (400kbps)

### **Key-Matrix Interface**

- Support up to 5\*5 key matrix

- Programmable Scan Period

- Support Long Key & Repeat Key

- Support up to Two Keys Pressed Simultaneously

- Support Keypad-Scan Wakeup function

### **Power Saving**

- Support Three Kind of Power Saving Mode: Standby, Suspend and Sleep Mode

- Support Wakeup Function by Host and External Event

### **Clock Source**

Embedded Programmable PLL for Core Clock, LCD Panel's Pixel Clock and Frame Buffer Clock

### Reset

- Provide Power On Reset Automatically

- Accept External Hardware Reset to Synchronize with System

- Software Command Reset

### **Power Supply**

- VDD: 3.3V +/- 0.3V

- Embedded 1.8V LDO

### Package

■ LQFP-128Pins, QFN-68Pins

### Temperature

■ -40°C~85°C

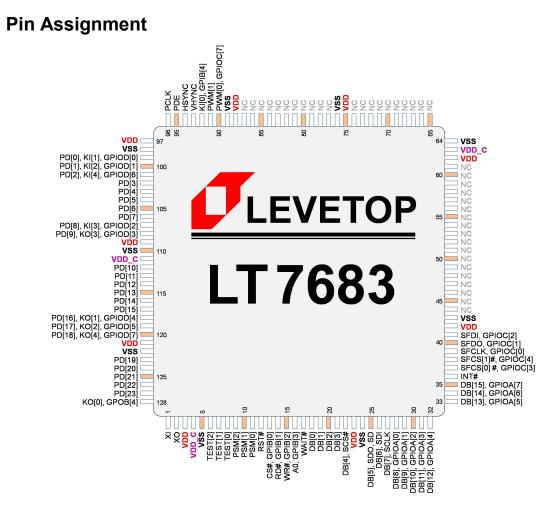

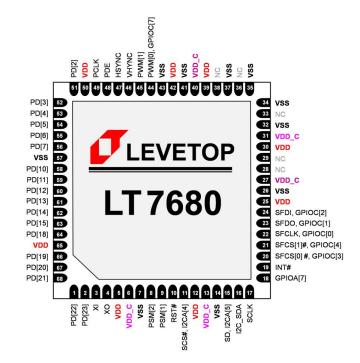

Figure A-4: LT7681/LT7683/LT7686 Pin Assignment (LQFP-128Pin)

Figure A-5: LT7680 Pin Assignment (QFN-68Pin)

### Pin Description -1 (LT7681/LT7683/LT7686/128Pin-LQFP)

LT7681/7683/7686 are 128Pin LQFP type package. The following tables are pin description of these chips.

### Host Interface Select Signals (3 Pins)

### Table A-2: Host I/F Select Signals

| Pin # | Pin Name      | I/O |         | Pin Description                  |                                                   |                                                 |  |     |                 |  |       |          |  |     |                 |

|-------|---------------|-----|---------|----------------------------------|---------------------------------------------------|-------------------------------------------------|--|-----|-----------------|--|-------|----------|--|-----|-----------------|

|       |               | Ι   | Host li | nterface Sel                     | ection                                            |                                                 |  |     |                 |  |       |          |  |     |                 |

|       |               |     |         | PSM[2:0]                         | Host I/F Mode                                     |                                                 |  |     |                 |  |       |          |  |     |                 |

|       | 9~11 PSM[2:0] |     | I       |                                  | 0 0 X                                             | 8bits or 16bits 8080 Parallel Interface<br>Mode |  |     |                 |  |       |          |  |     |                 |

| 9~11  |               |     |         |                                  | 0 1 X                                             | 8bits or 16bits 6800 Parallel Interface<br>Mode |  |     |                 |  |       |          |  |     |                 |

|       |               |     |         |                                  |                                                   |                                                 |  | 100 | 3-Wire SPI Mode |  |       |          |  |     |                 |

|       |               |     |         |                                  |                                                   |                                                 |  |     |                 |  |       |          |  | 101 | 4-Wire SPI Mode |

|       |               |     |         |                                  |                                                   |                                                 |  |     |                 |  | 1 1 X | I2C Mode |  |     |                 |

|       |               |     |         | t interface s<br>al interrupt in | set as parallel mode, then PSM[0] pin is put pin. |                                                 |  |     |                 |  |       |          |  |     |                 |

### Host Parallel I/F Signals (22 Pins)

### Table A-3: Host Parallel I/F Signals

| Pin #           | Pin Name             | I/O | Pin Description                                                                                                                                                                                                                                                                                                                                                                                          |

|-----------------|----------------------|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 35~25,<br>22~18 | DB[15:0]             | Ю   | Host Data Bus<br>These are data bus for data transfer between Host and LT768x.<br>DB[15:8] will become GPIO (GPIOA[7:0]) when parallel Host<br>8080/6800 16-bits data bus mode doesn't set.<br>DB[7:0] are multiplex pins that share with Serial Host control<br>pins. When serial host mode set then DB[7:0] are defined as the<br>control pins of serial host. Please refer to Host Interface section. |

| 13              | CS#<br>GPIB[0]       | I   | Chip Select Input<br>Low active chip select pin from Host.<br>If host interface set as serial host mode, then this pin can be set<br>as GPIB[0]. This pin with an internal pull-high resistor.                                                                                                                                                                                                           |

| 14              | RD#<br>EN<br>GPIB[1] | I   | <ul> <li>Read / Enable Input</li> <li>RD#: When host interface is 8080 mode then this is a Read input signal, active low.</li> <li>EN: When interface is 6800 mode then this is a Enable input signal, active high.</li> <li>If host interface set as serial host mode then this pin can be set as GPIB[1]. This pin with an internal pull-high resistor.</li> </ul>                                     |

| Pin # | Pin Name              | I/O | Pin Description                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|-------|-----------------------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15    | WR#<br>RW#<br>GPIB[2] | I   | <ul> <li>Write / Read-Write Input</li> <li>WR#: When host interface is 8080 mode then this is a Write input signal, active low.</li> <li>RW#: When interface is 6800 mode then this is a Read-Write input signal. It active high in 'Host's read cycle, and active low in Host's write cycle.</li> <li>If host interface set as serial host mode then this pin will be set as GPIB[2]. This pin with an internal pull-high resistor.</li> </ul> |

| 16    | A0<br>GPIB[3]         | I   | Command / Data Select Input<br>The pin is used to select Command or Data cycle.<br>A0 = 0, Status Read or Command Write cycle is selected.<br>A0 = 1, Data Read or Data Write cycle is selected.<br>If host interface set as serial host mode then this pin will be set<br>as GPIB[3]. This pin with an internal pull-high resistor.                                                                                                            |

| 36    | INT#                  | 0   | Interrupt Output Signal<br>The interrupt output for host to indicate the status.                                                                                                                                                                                                                                                                                                                                                                |

| 17    | WAIT#                 | 0   | Wait Output Signal<br>When high, it indicates that the LT768x is ready to transfer data.<br>When low, then microprocessor is in wait state.                                                                                                                                                                                                                                                                                                     |

### Table A-3: Host MCU Parallel I/F Signals (Continued)

### MCU Serial I/F Signals (8 Pins)

### Table A-4: Host Serial I/F Signals

| Pin # | Pin Name                        | I/O | Pin Description                                                                                                                                                                                                                                                                                                                                              |

|-------|---------------------------------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 27    | SCLK<br>(DB[7])                 | I   | <b>SPI or I2C Clock</b><br><b>SCLK</b> : Clock of 3-wire, 4-wire Serial or I2C interface.<br>This is a multiplex pin that share with Parallel Host Data Bus DB[7].                                                                                                                                                                                           |

| 26    | SDI<br>I2C_SDA<br>(DB[6])       | I   | <ul> <li>I2C Data / 4-wire SPI Data Input</li> <li>SDI: Data input pin of 4-wire SPI I/F. Connect to MCU's MOSI.</li> <li>I2C_SDA: Bi-direction data pin of I2C I/F.</li> <li>This pin is not used In 3-Wire serial I/F. Please connect it to GND. This is a multiplex pin that share with Parallel Host Data Bus DB[6].</li> </ul>                          |

| 25    | SD<br>SDO<br>I2CA[5]<br>(DB[5]) | Ю   | <ul> <li>3-wire SPI Data / 4-wire SPI Data Output / I2C Slave Address Select</li> <li>SD: Bi-direction data pin of 3-wire SPI I/F.</li> <li>SDO: Data output pin of 4-wire SPI I/F. Connect to MCU's MISO.</li> <li>I2CA[5]: I2C device address bit[5] of I2C I/F.</li> <li>This is a multiplex pin that share with Parallel Host Data Bus DB[5].</li> </ul> |

| Pin # | Pin Name                   | I/O | Pin Description                                                                                                                                                                                                                                            |

|-------|----------------------------|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 22    | SCS#<br>I2CA[4]<br>(DB[4]) | I   | <ul> <li>SPI Chip Select / I2C Slave Address Select</li> <li>SCS#: Chip select pin for 3-wire or 4-wire serial I/F.</li> <li>I2CA[4]: I2C device address bit[4].</li> <li>This is a multiplex pin that share with Parallel Host Data Bus DB[4].</li> </ul> |

| 21~18 | I2CA[3:0]<br>(DB[3:0])     | I   | I2C Slave Address Select<br>I2CA[3:0]: I2C device address bit [3:0].<br>These pins are not used In 3-Wire or 4-Wire I/F. Please connect<br>them to GND.<br>These are multiplex pins that share with Parallel Host Data Bus<br>DB[3:0].                     |

### Table A-4: Host Serial I/F Signals (Continued)

### External Serial Flash / SPI Master Signals (5 Pins)

| Pin # | Pin Name             | I/O | Pin Description                                                                                                                                                                                                                                                                                                                                                 |

|-------|----------------------|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 37    | SFCS[0]#<br>GPIOC[3] | Ю   | Chip Select 0 for External Serial Flash or SPI device<br>SPI Chip select pin #0 for serial Flash or SPI device.<br>If SPI master I/F is disabled then it can be programmed as<br>GPIOC[3], and default is input function.                                                                                                                                       |

| 38    | SFCS[1]#<br>GPIOC[4] | Ю   | Chip Select 1 for External Serial Flash or SPI device<br>SPI Chip select pin #1 for serial Flash or SPI device.<br>If SPI master I/F is disabled then it can be programmed as<br>GPIOC[4], and default is input function.                                                                                                                                       |

| 39    | SFCLK<br>GPIOC[0]    | Ю   | <b>SPI Serial Clock</b><br>Serial clock output for serial Flash/ROM or SPI device.<br>If SPI master I/F is disabled then it can be programmed as GPIO<br>C[0], and default is input function.                                                                                                                                                                   |

| 40    | SFDO<br>GPIOC[1]     | Ю   | <ul> <li>Master Output Slave Input</li> <li>Single Mode: Data input of serial Flash or SPI device. For LT768, it is output.</li> <li>Dual Mode: The signal is used as bi-direction data #0(SIO0). Only valid in serial flash DMA mode.</li> <li>If SPI master I/F is disabled then it can be programmed as GPIO C[1], and default is input function.</li> </ul> |

| 41    | SFDI<br>GPIOC[2]     | Ю   | <ul> <li>Master Input Slave Output</li> <li>Single Mode: Data output of serial Flash or SPI device. For LT768, it is input.</li> <li>Dual Mode: The signal is used as bi-direction data #1(SIO1). Only valid in serial flash DMA mode.</li> <li>If SPI master I/F is disabled then it can be programmed as GPIOC[2], and default is input function.</li> </ul>  |

### LCD Driver Signals (28 Pins)

### Table A-6: LCD Driver Signals

| Pin #              | Pin Name | I/O |            | Pin Description |                   |                 |                 |                                     |    |  |

|--------------------|----------|-----|------------|-----------------|-------------------|-----------------|-----------------|-------------------------------------|----|--|

|                    |          |     | TF1<br>64M | (/256K/16.7     | a bus outpu       | epth by re      | egister sett    | .T76x suppo<br>ting; user c<br>ing. |    |  |

|                    |          |     |            | Pin             | TFT-LCD Interface |                 |                 |                                     |    |  |

|                    |          |     |            | Name            | 11b<br>(GPIO)     | 10b<br>(16bits) | 01b<br>(18bits) | 00b<br>(24bits)                     |    |  |

|                    |          |     |            | PD[0]           | GI                | PIOD[0] / KI    | [1]             | B0                                  |    |  |

|                    |          |     |            | PD[1]           | GI                | PIOD[1] / KI    | [2]             | B1                                  |    |  |

|                    |          |     |            | PD[2]           | GPIOD[            | 6] / KI[4]      | B0              | B2                                  |    |  |

|                    |          |     |            | PD[3]           | GPIOE[0]          | B0              | B1              | B3                                  |    |  |

|                    |          |     |            | PD[4]           | GPIOE[1]          | B1              | B2              | B4                                  |    |  |

|                    |          |     |            | PD[5]           | GPIOE[2]          | B2              | B3              | B5                                  |    |  |

|                    |          |     |            | PD[6]           | GPIOE[3]          | B3              | B4              | B6                                  |    |  |

|                    |          | IO  |            | PD[7]           | GPIOE[4]          | B4              | B5              | B7                                  |    |  |

|                    |          |     |            | PD[8]           | GPIOD[2] / KI[3]  |                 | G0              |                                     |    |  |

| 127~123,           | וטיגגוטט |     |            | PD[9]           | GPIOD[3] / KO[3]  |                 | G1              |                                     |    |  |

| 120~112,<br>108~99 | PD[23:0] |     |            | PD[10]          | GPIOE[5]          | G0              | G0              | G2                                  |    |  |

|                    |          |     |            | PD[11]          | GPIOE[6]          | G1              | G1              | G3                                  |    |  |

|                    |          |     |            |                 | PD[12]            | GPIOE[7]        | G2              | G2                                  | G4 |  |

|                    |          |     |            | PD[13]          | GPIOF[0]          | G3              | G3              | G5                                  |    |  |

|                    |          |     |            | PD[14]          | GPIOF[1]          | G4              | G4              | G6                                  |    |  |

|                    |          |     |            | PD[15]          | GPIOF[2]          | G5              | G5              | G7                                  |    |  |

|                    |          |     |            | PD[16]          | GF                | PIOD[4] / KC    | <b>[</b> 1]     | R0                                  |    |  |

|                    |          |     |            | PD[17]          | GP                | IOD[5] / KC     | l[2]            | R1                                  |    |  |

|                    |          |     |            | PD[18]          | GPIOD[7           | 7] / KO[4]      | R0              | R2                                  |    |  |

|                    |          |     |            | PD[19]          | GPIOF[3]          | R0              | R1              | R3                                  |    |  |

|                    |          |     |            | PD[20]          | GPIOF[4]          | R1              | R2              | R4                                  |    |  |

|                    |          |     |            | PD[21]          | GPIOF[5]          | R2              | R3              | R5                                  |    |  |

|                    |          |     |            | PD[22]          | GPIOF[6]          | R3              | R4              | R6                                  |    |  |

|                    |          |     |            | PD[23]          | GPIOF[7]          | R4              | R5              | R7                                  |    |  |

|                    |          |     | pins       | s. The Defa     |                   | of LCD I/F is   | s 18bpp fun     | and Key-Ma<br>action mode,          |    |  |

| Pin # | Pin Name | I/O | Pin Description                                                                                         |

|-------|----------|-----|---------------------------------------------------------------------------------------------------------|

| 96    | PCLK     | Ο   | Panel Scan Clock<br>Generic TFT interface signal for panel scan clock. It derives from<br>internal PLL. |

| 93    | VSYNC    | 0   | VSYNC Pulse<br>Generic TFT interface signal for vertical synchronous pulse.                             |

| 94    | HSYNC    | 0   | <b>HSYNC Pulse</b><br>Generic TFT interface signal for horizontal synchronous pulse.                    |

| 95    | PDE      | 0   | <b>Data Enable</b><br>Generic TFT interface signal for data valid or data enable.                       |

### Table A-6: LCD Driver Signals (Continued)

### **PWM Output Signals (2 Pins)**

### Table A-7: PWM Output Signals

| Pin # | Pin Name                              | I/O | Pin Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|-------|---------------------------------------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 90    | PWM[0]<br>INITDIS<br>GPIOC[7]<br>CCLK | Ю   | <ul> <li>PWM Output 0 / Initial Display Enable</li> <li>PWM[0]: PWM's output signal. The output mode is decided by configuration register. This pin can be used as the control signal of TFT panel's back light.</li> <li>INITDIS: Pull-high this pin will enable Initial Display function. This pin has internal pull-down in reset period to disable Initial Display function by default. i.e. after reset complete, internal pull-down resistor will be disabled.</li> <li>If PWM function disabled then it can be programmed as GPIO C[7], and default is GPIOC[7] input function, or output Core Clock - CCLK.</li> </ul> |

| 91    | PWM[1]                                | Ю   | <b>PWM Output 1</b><br>PWM's output signal. The output mode and output function is<br>decided by configuration register. This pin also can be used as<br>the control signal of TFT panel's back light.<br>When TEST[0] set high, then PWM[1] pin is external panel scan<br>clock input                                                                                                                                                                                                                                                                                                                                         |

# *J*LT768x

### **GPIO Signals** (28 Pins)

Table A-8: General Purpose I/O Signals

| Pin #                                       | Pin Name                          | I/O | Pin Description                                                                                                                                                                                                                                                                                                                      |

|---------------------------------------------|-----------------------------------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 35~28                                       | GPIOA[7:0]                        | Ю   | <b>GPIO A Group</b><br>These are general purpose I/O.<br>These are multiplex pins that share with DB[15:8]. They are<br>available when 8bits parallel host mode and serial Host mode.                                                                                                                                                |

| 92,<br>128,<br>16~13                        | GPIB[4],<br>GPOB[4],<br>GPIB[3:0] | Ю   | GPIO B Group<br>These are general purpose I/O. GPIB[3:0] are read only and<br>available in serial host mode.<br>GPIB[4] is same pin with KI[0].<br>GPOB[4] is same pin with KO[0].<br>GPIB[3:0] are multiplex pins that share with {A0, WR#, RD#,<br>CS#}.                                                                           |

| 90, 38,<br>37,<br>41~39                     | GPIOC[7],<br>GPIOC[4:0]           | 10  | GPIO C Group<br>These are general purpose I/O. GPIOC are available when<br>PWM and SPI Master functions disabled.<br>GPIOC[7] is same pin with PWM[0].<br>GPIOC[4:0] are multiplex pins that share with {SFCS1#,<br>SFCS0#, SFDI, SFDO, SFCLK}                                                                                       |

| 120, 101<br>119, 118<br>108, 107<br>100, 99 | GPIOD[7:0]                        | Ю   | <ul> <li>GPIO D Group</li> <li>These are general purpose I/O.</li> <li>GPIOD[7:0] are multiplex pins that share with PD[18, 2, 17, 16, 9, 8, 1, 0].</li> <li>GPIOD[5,4,3,2,1,0] are available when LCD Panel interface is set 16bits or 18bits.</li> <li>GPIOD[7,6] are available when LCD Panel interface is set 16bits.</li> </ul> |

### Key-Matrix Signals (10 Pins)

Table A-9: Key-Matrix Signals

| Pin #                       | Pin Name | I/O | Pin Description                                                                                                                                                                                                                                                                                                      |

|-----------------------------|----------|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 101, 107,<br>100, 99,<br>92 | KI[4:0]  | I   | <ul> <li>Key-Matrix Data Pins</li> <li>Keypad data inputs with internal pull-up resister.</li> <li>KI[4:1] are multiplex pins that share with PD[8] and PD[2:0]. The Key-matrix function will be disable when LCD I/F are set as 24bits.</li> <li>XKIN[0] also provide the I2CMCK function of I2C Master.</li> </ul> |

| 120,108,<br>119,118,<br>128 | KO[4:0]  | Ο   | <b>Key-Matrix Strobe Pins</b><br>Keypad strobe data outputs with Open-Drain.<br>KO[4:1] are multiplex pins that share with PD[9] and PD[18:16].<br>KO[0] also provide the I2CMDA function of I2C Master.                                                                                                             |

### Power and Clock Signals (23 Pins)

### Table A-10: Power and Clock Signals

| Pin #                                           | Pin Name | I/O | Pin Description                                                                                                                                                                                                                         |

|-------------------------------------------------|----------|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1                                               | XI       | I   | <b>Crystal / External Clock Input</b><br>This input pin is used for internal crystal circuit or external clock<br>that generate clock source for PLL. It should be connected to<br>external crystal and suggested frequency is 10.0MHz. |

| 2                                               | ХО       | 0   | <b>Crystal Output</b><br>This is an output pin for internal crystal circuit. It should be<br>connected to external crystal circuit.                                                                                                     |

| 4, 63,<br>111                                   | VDD_C    | PWR | Internal LDO Output<br>These pins must connect 1uF and 0.1uF capacitor to ground.                                                                                                                                                       |

| 3, 23,<br>42, 62,<br>75, 88,<br>97, 109,<br>121 | VDD      | PWR | 3.3V Power Pins                                                                                                                                                                                                                         |

| 5, 24,<br>43, 64,<br>76, 89<br>98, 110,<br>122  | VSS      | PWR | Ground(GND) Pins                                                                                                                                                                                                                        |

### **Reset and Test Signals (4 Pins)**

### Table A-11: Reset and Test Signals

| Pin # | Pin Name  | I/O | Pin Description                                                                                                                                                                                                                                                                                                                                  |

|-------|-----------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 12    | RST#      | I/O | <b>Reset Signal Input</b><br>This is a active low Reset pin for LT768x. To avoid noise<br>interfere and cause fake reset behavior, this pin is active at least<br>256 OSC clocks.                                                                                                                                                                |

| 6~8   | TEST[2:0] | I   | Test InputThese pins are used for testing and normally connect to GND.If TEST[0]keep high, the internal PLL will be disable and thesystem clock is supply by external.If TEST[2:1]keep 01b, then the SPI Master signals will keepfloating. This feature allow external device to program SerialFlash directly. (i.e. ISP, In-System-Programming) |

## Pin Description -2 (LT7680/68Pin-QFN)

LT7680 is a 68Pin QFN type package chip. The following tables are their pins function list. For detail pins description, please refer to the previous section - Pin Description -1.

### Host Interface Select Signals (2 Pins)

### Table A-12: Host I/F Select Signals

| Pin # | Pin Name | I/O | Pin Description                                                                                                                                                                                                                                                          |

|-------|----------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 8~9   | PSM[2:1] | I   | Host Interface Selection<br>LT7680 only supports 3-Wires SPI and I2C mode. Its PSM[0] pin<br>already connected to GND within the IC, while PSM[2] must<br>pull-up to VDD.<br>When PSM[1] = 0, select serial 3-line SPI mode.<br>When PSM[1] = 1, select serial I2C mode. |

### Host Serial I/F Signals (5 Pins)

### Table A-13: Host Serial I/F Signals

| Pin # | Pin Name        | I/O | Pin Description                                                        |

|-------|-----------------|-----|------------------------------------------------------------------------|

| 17    | SCLK            | Ι   | SPI or I2C Clock                                                       |

| 16    | I2C_SDA         | Ι   | I2C Data / 4-wire SPI Data Input                                       |

| 15    | SD<br>I2CA[5]   | IO  | 3-wire SPI Data / 4-wire SPI Data Output / I2C Slave Address<br>Select |

| 11    | SCS#<br>I2CA[4] | I   | SPI Chip Select / I2C Slave Address Select                             |

| 19    | INT#            | 0   | Interrupt Output Signal                                                |

### LCD Driver Signals (22 Pins)

### Table A-14: LCD Driver Signals

| Pin #  | Pin Name   | I/O | Pin Description    |

|--------|------------|-----|--------------------|

| 2~1,   |            |     |                    |

| 68~66, | PD[23:18], |     |                    |

| 64,    | PD[15:10], | IO  | LCD Panel Data Bus |

| 63~58, | PD[7:2],   |     |                    |

| 56~51  |            |     |                    |

| 49     | PCLK       | 0   | Panel Scan Clock   |

| 46     | VSYNC      | 0   | VSYNC Pulse        |

| 47     | HSYNC      | 0   | HSYNC Pulse        |

| 48     | PDE        | 0   | Data Enable        |

### External Serial Flash / SPI Master Signals (5 Pins)

Table A-15: External Serial Flash Signals

| Pin # | Pin Name   | I/O | Pin Description                                       |

|-------|------------|-----|-------------------------------------------------------|

| 21~20 | SFCS[1:0]# | IO  | Chip Select 0 for External Serial Flash or SPI device |

| 22    | SFCLK      | IO  | SPI Serial Clock                                      |

| 23    | SFDO       | IO  | Master Output Slave Input                             |

| 24    | SFDI       | IO  | Master Input Slave Output                             |

### **PWM Output Signals (2 Pins)**

### Table A-16: PWM Output Signals

| Pin # | Pin Name | I/O | Pin Description                       |

|-------|----------|-----|---------------------------------------|

| 45    | PWM[0]   | 10  | PWM Output 0 / Initial Display Enable |

| 44    | PWM[1]   | 10  | PWM Output 1                          |

### **GPIO Signals** (7 Pins)

Table A-17: General Purpose I/O Signals

| Pin #                        | Pin Name               | I/O | Pin Description |

|------------------------------|------------------------|-----|-----------------|

| 18                           | GPIOA[7]               | IO  | GPIO A Group    |

| 44, 21,<br>20, 24,<br>23, 22 | GPIOC[7]<br>GPIOC[4:0] | IO  | GPIO C Group    |

### Reset (1 Pins)

### Table A-18: Reset Signal

| Pin # | Pin Name | I/O | Pin Description    |

|-------|----------|-----|--------------------|

| 10    | RST#     | I/O | Reset Signal Input |

### Power and Clock Signals (26 Pins)

Table A-19: Power and Clock Signals

| Pin #                                              | Pin Name    | I/O | Pin Description                                       |

|----------------------------------------------------|-------------|-----|-------------------------------------------------------|

| 2                                                  | XI          | Ι   | Crystal / External Clock Input                        |

| 3                                                  | ХО          | 0   | Crystal Output                                        |

| 36, 13,<br>27, 31,<br>40                           | VDD_C       | PWR | Internal LDO Output                                   |

| 5, 12,<br>25, 30,<br>39, 42,<br>50, 65             | VDD         | PWR | 3.3V Power Pins                                       |

| 7, 14,<br>26, 32,<br>34, 35,<br>37, 41,<br>43, 57, | VSS         | PWR | Ground(GND) Pins                                      |

|                                                    | Thermal Pad | -   | The back of LT7680 Heat sink pad must tied to ground. |

The LT768x series support different Host interfaces. For example, the LT7680 is a 68pin QFN chip , which only supports serial SPI and I2C mode. The following table is Host interface supporting list for LT768x series:

| No. | Host Interface Mode                 | LT7681<br>LT7683<br>LT7686 | LT7680A<br>LT7680B |

|-----|-------------------------------------|----------------------------|--------------------|

| 1   | 8bits 8080 Parallel Interface Mode  | v                          |                    |

| 2   | 16bits 8080 Parallel Interface Mode | v                          |                    |

| 3   | 8bits 6800 Parallel Interface Mode  | V                          |                    |

| 4   | 16bits 6800 Parallel Interface Mode | V                          |                    |

| 5   | 3-Wire SPI Mode                     | v                          | v                  |

| 6   | 4-Wire SPI Mode                     | V                          |                    |

| 7   | I2C Mode                            | V                          | v                  |

Table A-20: Host Interface Supporting List of LT768x Series

## Package Information

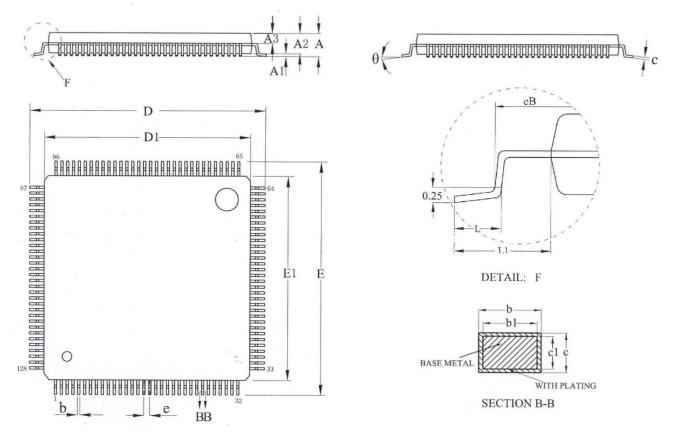

### ■ LT7681/LT7683/LT7686 (LQFP-128pin)

Figure B-1: 128Pin LQFP Outline

| Symbol | Millimeter |       |      | Symbol | Millimeter |      |       |

|--------|------------|-------|------|--------|------------|------|-------|

| Symbol | Min.       | Nom.  | Max  | Symbol | Min.       | Nom. | Max   |

| Α      | -          | -     | 1.60 | D1     | 13.9       | 14.0 | 14.1  |

| A1     | 0.05       | -     | 0.15 | E      | 15.8       | 16.0 | 16.2  |

| A2     | 1.35       | 1.40  | 1.45 | E1     | 13.9       | 14.0 | 14.1  |

| A3     | 0.59       | 0.64  | 0.69 | eB     | 15.05      | -    | 15.35 |

| b      | 0.14       | -     | 0.22 | е      | 0.40BSC    |      |       |

| b1     | 0.13       | 0.16  | 0.19 | L      | 0.45       | -    | 0.75  |

| С      | 0.13       | -     | 0.17 | L1     | 1.00REF    |      |       |

| c1     | 0.12       | 0.13  | 0.14 | θ      | 0          |      | 7     |

| D      | 15.8       | 16.00 | 16.2 |        |            |      |       |

Table B-1: 128Pin LQFP Dimension

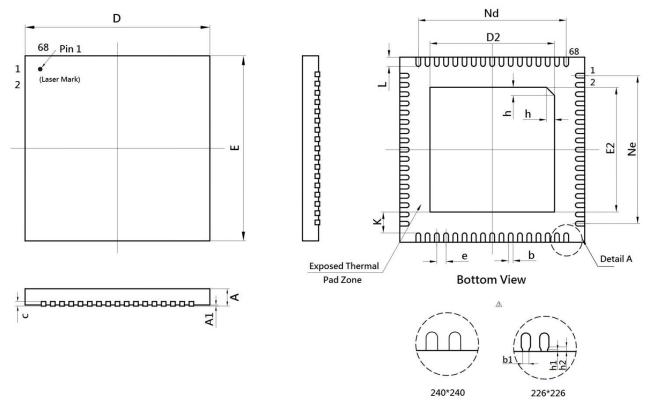

### ■ LT7680 (QFN-68pin)

Figure B-2: 68Pin QFN Outline

Note: When PCB layout, the heat pad of LT7680's back (thermal Pad Zone) must be directly grounded.

| Symbol    | Millimeter |         |      | Symbol | Millimeter |      |      |

|-----------|------------|---------|------|--------|------------|------|------|

|           | Min.       | Nom.    | Max  | Symbol | Min.       | Nom. | Max  |

| Α         | 0.70       | 0.75    | 0.8  | E      | 7.9        | 8.0  | 8.10 |

| A1        | -          | 0.02    | 0.05 | Ne     | 6.40BSC    |      |      |

| b         | 0.15       | 0.20    | 0.25 | L      | 0.35       | 0.40 | 0.45 |

| <b>b1</b> | 0.14REF    |         |      | K      | 0.20       | -    | -    |

| С         | 0.18       | 0.20    | 0.25 | h      | 0.30       | 0.35 | 0.40 |

| D         | 7.90       | 8.00    | 8.10 | h1     | 0.04REF    |      |      |

| е         | 0.40BSC    |         |      | h2     | 0.10REF    |      |      |

| Nd        |            | 6.40BSC |      |        |            |      |      |

Table B-2: 68Pin QFN Dimenstion

Table B-3: Lead Frame Dimension

| L/F 载体尺寸 | Symbol | Millimeter   | L/F<br>Dimension | Symbol | Millimeter   |

|----------|--------|--------------|------------------|--------|--------------|

| 240*240  | D2     | 5.49+/- 0.10 | 226*226          | D2     | 5.39+/- 0.10 |

|          | E2     | 5.49+/- 0.10 | 220 220          | E2     | 5.39+/- 0.10 |